DSD DAC迷思和現況

說實話在下發這篇其實會傷害到很多廠商的利益,

不過在下還是說忍不住想打破這種謊言,

在下有發言,DSD現在還不成熟,

也有發篇DAC的迷思,目前DSD基本都是用PCM來做,

不管是撥放還是編輯剪接甚至錄製,

所以DSD DAC目前只是噱頭。

錄製剪輯方面

DXD的定義

DSD原始錄音一般都需要在工作室進行再次轉換到高bit PCM進行編輯后再還原成DSD。

又或者是用高bit PCM作為原始錄音後再進行編輯處理,之後再轉換成DSD。

DXD只是一種錄音方式,也是PCM的一種,在DXD格式上進行編輯處理混音之後再轉換成DSD發售。說實話DSD原始錄音一般不直接用于發行SACD,因為DSD 1bit 錄音沒辦法進行編輯等後期處理,所以才誕生了DXD錄音方式。

DXD錄音-後期處理-再轉換為DSD-壓制SACD-售賣,這就是為什么有的SACD碟片上有DXD的標志,也有CD上有DXD標志,DXD只是一種錄音方式而已,最終發行不外乎SACD-DSD,DVD-A24-96,24-192,CD-WAV而已。

解碼方面

現在基本DSD解碼是換成PCM输出然後再解碼

ES9018的DSD是通過內部DSP轉換成PCM输出

除了少數幾家,基本上市面上都是這樣做,

所以基本聽到都是PCM的東西,

當然廠商一定會主打能解DSD,

但是嚴格來說聽到的聲音絕對不是DSD。

真正數位 DAC定義

真正DSD和PWM是沒解碼晶片

只用低通濾波器(LPF Low-pass filter)

所以說真正DSD和PWM的DAC應該是用DSP把PCM轉成DSD或PWM

然後用LPF而不是像現在的相反

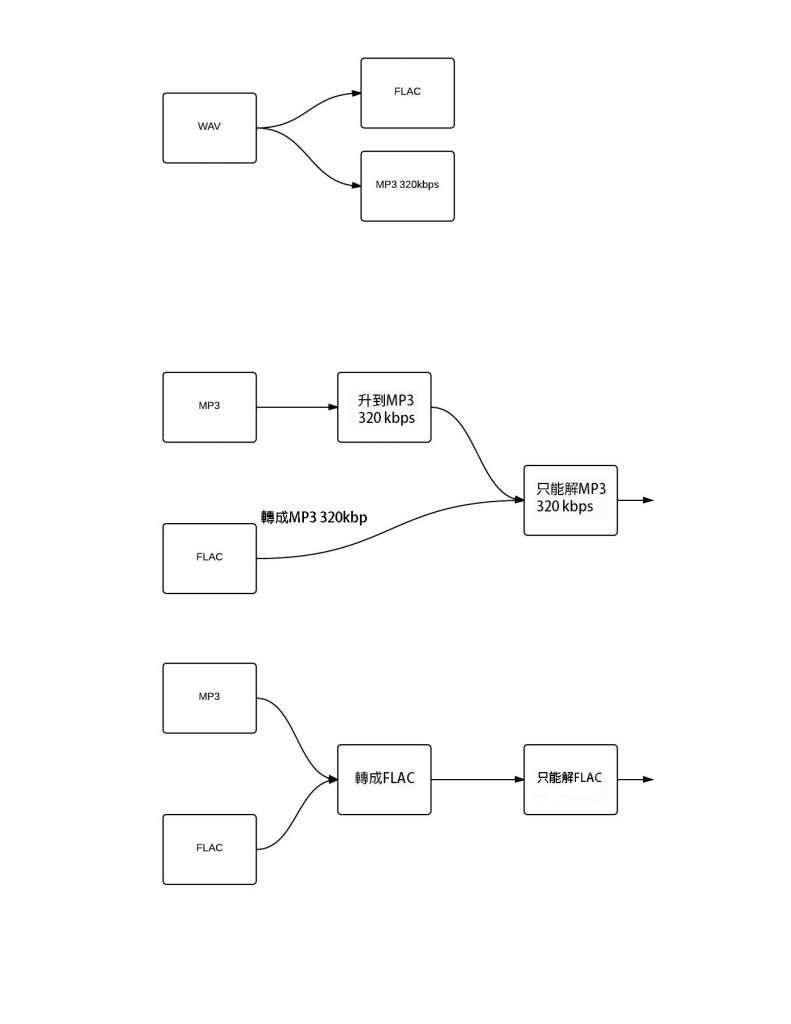

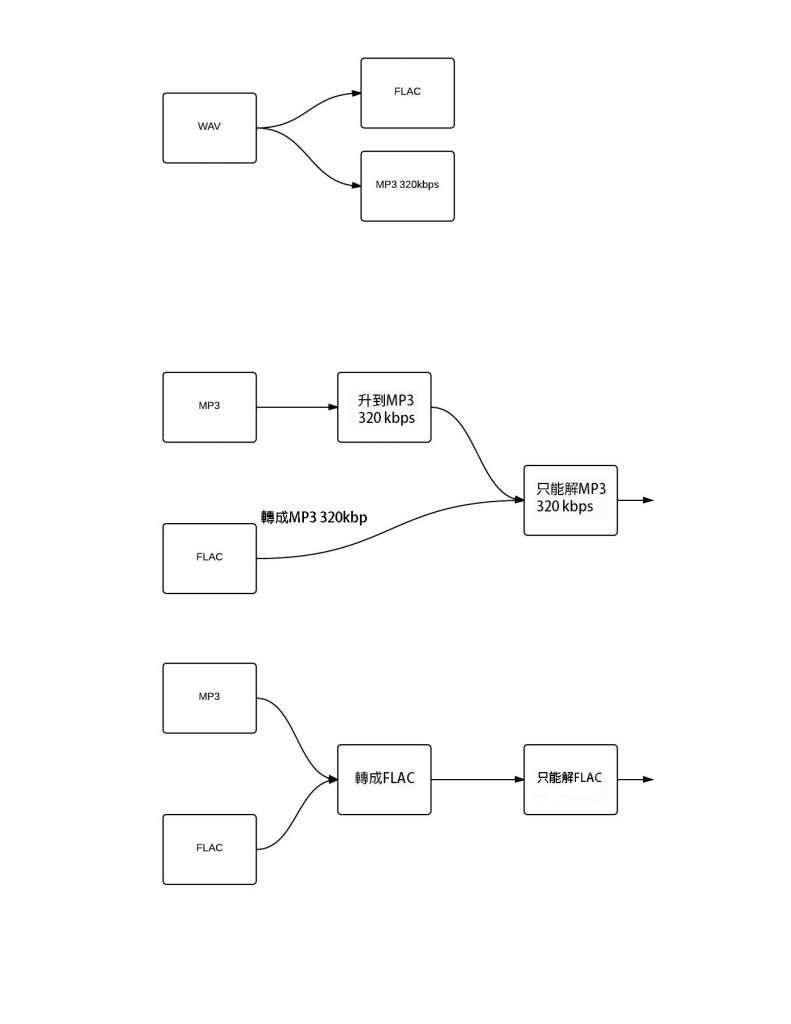

DXD(高bit PCM)=wav

DSD =flac

PCM=MP3

自行作出的比喻說明圖

附上AK4399的圖http://www.asahi-kasei.co.jp/akm/en/product/ak4399/ak4399.html

結論

在下是理解廠商這樣做的原因,

畢竟單做一個DSP比重做整個晶片省時省力也更保險,

有些廠商更只要外接一個DSP晶片就可以撥DSD,

這種方法比內置DSP風險更大,

反正沒真去比較耳朵根本聽不出來,

當然有些人會說現在這種變相PCM(DSD)真實好聽 ,

這是當然因為這種變相PCM(DSD)其實就是把DSP當輸出,

然後直連到解碼,少了一堆有的沒的當然比較真實好聽,

不過還是比真的DSD和PWM差很多,

不過在下還是說忍不住想打破這種謊言,

在下有發言,DSD現在還不成熟,

也有發篇DAC的迷思,目前DSD基本都是用PCM來做,

不管是撥放還是編輯剪接甚至錄製,

所以DSD DAC目前只是噱頭。

錄製剪輯方面

DXD的定義

DSD原始錄音一般都需要在工作室進行再次轉換到高bit PCM進行編輯后再還原成DSD。

又或者是用高bit PCM作為原始錄音後再進行編輯處理,之後再轉換成DSD。

DXD只是一種錄音方式,也是PCM的一種,在DXD格式上進行編輯處理混音之後再轉換成DSD發售。說實話DSD原始錄音一般不直接用于發行SACD,因為DSD 1bit 錄音沒辦法進行編輯等後期處理,所以才誕生了DXD錄音方式。

DXD錄音-後期處理-再轉換為DSD-壓制SACD-售賣,這就是為什么有的SACD碟片上有DXD的標志,也有CD上有DXD標志,DXD只是一種錄音方式而已,最終發行不外乎SACD-DSD,DVD-A24-96,24-192,CD-WAV而已。

解碼方面

現在基本DSD解碼是換成PCM输出然後再解碼

ES9018的DSD是通過內部DSP轉換成PCM输出

除了少數幾家,基本上市面上都是這樣做,

所以基本聽到都是PCM的東西,

當然廠商一定會主打能解DSD,

但是嚴格來說聽到的聲音絕對不是DSD。

真正數位 DAC定義

真正DSD和PWM是沒解碼晶片

只用低通濾波器(LPF Low-pass filter)

所以說真正DSD和PWM的DAC應該是用DSP把PCM轉成DSD或PWM

然後用LPF而不是像現在的相反

DXD(高bit PCM)=wav

DSD =flac

PCM=MP3

自行作出的比喻說明圖

附上AK4399的圖http://www.asahi-kasei.co.jp/akm/en/product/ak4399/ak4399.html

結論

在下是理解廠商這樣做的原因,

畢竟單做一個DSP比重做整個晶片省時省力也更保險,

有些廠商更只要外接一個DSP晶片就可以撥DSD,

這種方法比內置DSP風險更大,

反正沒真去比較耳朵根本聽不出來,

當然有些人會說現在這種變相PCM(DSD)真實好聽 ,

這是當然因為這種變相PCM(DSD)其實就是把DSP當輸出,

然後直連到解碼,少了一堆有的沒的當然比較真實好聽,

不過還是比真的DSD和PWM差很多,